HP200

Z topologicznego punktu widzenia chip został podzielony na część brzegową z magistralami brzegowymi Ucc i GND oraz z przetwornikami wejścia i wyjścia, które zostały równomiernie rozmieszczone na całym obwodzie chipa.

Tranzystor wejściowy podzielono na jednostki dwuemiterowe, które można było łączyć w celu uzyskania bramek o 2, 4, 6 i 8 wejściach. Bramy zostały zaprojektowane z otwartymi kolektorami, aby stworzyć konstrukcje skrzyżowań ORAZ.

Sama matryca bramkowa została zlokalizowana wewnątrz obszaru chipa wyznaczonego przez przetworniki wejścia-wyjścia. W sumie 240 bramek podzielono na macierz 6 x 40 bramek. Każdy pasek 40 bramek zasilany był z osobnego stabilizatora napięcia, umieszczonego na końcu paska bramek. Pas bram otoczony jest z obu stron dwoma rzędami zarezerwowanych przestrzeni dla połączenia bramek w osi X na pierwszym poziomie metalicznym. W środku matrycy, pomiędzy dwoma rzędami miejsc na połączenia X, zarezerwowano miejsce na główną szynę naziemną. Dalsze połączenia pomiędzy bramkami można wykonać w kierunku Y w zarezerwowanych przestrzeniach drugiego poziomu metalicznego. Typowe opóźnienie jednej bramki wewnętrznej wynosiło 2,5 ns, typowe opóźnienie przetwornika wejściowego wynosiło 2,0 ns, a przetwornika wyjściowego 6 ns. Zewnętrzne parametry statyczne odpowiadały układom scalonym TTL.

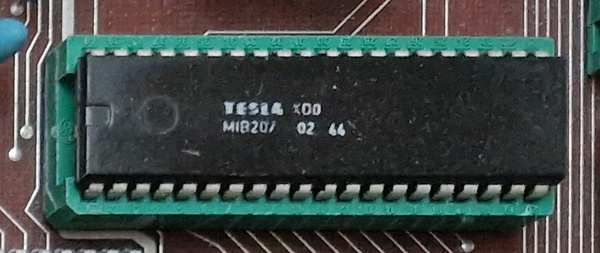

Obwody MIB i MIC201 - 207 to wstępnie zaprogramowane macierze bramek. Zgodnie z tym oznaczeniem znany jest jedynie rozmiar obudowy i temperatura robocza, do której można używać tego IO. Na każdym obwodzie serii MIB/MIC201-207 oprócz kodu produkcyjnego znajdują się cztery dodatkowe cyfry. Te cztery cyfry określają, jaki rodzaj chipa znajduje się w środku i co potrafi dane IO. Znam kody + opis funkcji od numeru 0202 do 0249.

MIB-obudowa z tworzywa sztucznego 0 do 70 stopni C.

Obudowa MIC-ceramiczna -55 do 125 stopni C.

201 - 14 placówek

202 - 16 placówek

203 - 18 placówek

204 - 20 placówek

205 - 24 placówki

206 - 28 placówek

207 - 40 placówek

Częściowo niestandardowe układy scalone oparte na HP 200

Np. HP202, HP216, HP226 i HP227

- zarządzanie pamięciami półprzewodnikowymi

- sterowanie autobusem

- wsparcie automatyzacji

- MIB207/0231 obsługuje obwód logiczny procesora z I8088, zawiera logikę wstawiania WAIT w mikroprocesorze i dekoder adresu pamięci procesora. Plastikowa obudowa 40pin.

- MIB204/0217 8-bitowy dwukierunkowy licznik z rejestrem ustawiania danych i porównaniem z wyprowadzoną równoważnością i rejestrem 8-bitowym. Wyjścia trójstanowe. Plastikowa obudowa 20pin.

Używany m.in. dla portu równoległego w komputerze TNS HC-16.

Do zaprojektowania HP 200 początkowo wykorzystano zmodyfikowany system projektowania płytek drukowanych ISAN 1. Część sprzętowa tego systemu obejmowała procesor SM 4-20, 256 KB RAM, pamięć kasetową CM 5400, pamięć na taśmie magnetycznej CM 5300, CM 7202 terminal operatorski, wyświetlacz graficzny CM 7405 i drukarka mozaiki graficznej Consul 2111.

System testowy

System testowy TADA 4 przeznaczony jest do badań funkcjonalnych oraz pomiaru parametrów statycznych i dynamicznych cyfrowych układów scalonych o max. liczba wyjść wynosi 40. Sterowanie testerem odbywa się za pomocą komputera osobistego PP-06-2.